晶振官方博客

更多>>低抖動在Pletronics Oscillator高性能設(shè)計中的重要性

來源:http://tqlwapf.cn 作者:康華爾電子 2019年08月01

現(xiàn)在的石英晶體振蕩器都往高性能方向設(shè)計,那什么樣的振蕩器才稱得上高性能呢?普通的振蕩器不屬于高性能,所謂的高性能指的是具備特殊的低相位抖動,低相位噪聲,低G靈敏度,寬溫,頻率范圍大,頻率偏差精準(zhǔn)度高的,才能被稱做高性能.主要應(yīng)用到高速串行,以太網(wǎng),局域網(wǎng),蜂窩,無線,通信,軍工等多種高端領(lǐng)域,本文主要為大家講解,低抖動在高性能的Pletronics Oscillator設(shè)計中有多重要,Pletronics晶振公司是美國知名的晶體振蕩器制造商.

高速串行總線架構(gòu)是當(dāng)今高性能設(shè)計的標(biāo)準(zhǔn).雖然并行總線標(biāo)準(zhǔn)正在發(fā)生一些變化,但串行總線在多個市場和設(shè)備上建立-計算機,手機,娛樂系統(tǒng)等.串行總線在電路和電路板布局中提供了性能優(yōu)勢和設(shè)計簡化(更少的跡線).串行數(shù)據(jù)鏈路表現(xiàn)為當(dāng)今知情世界的動脈,因為它們在處理系統(tǒng)中將數(shù)據(jù)從一個點傳輸?shù)搅硪粋€點.為了確保準(zhǔn)確的傳送和接收,數(shù)字系統(tǒng)中的數(shù)據(jù)由時鐘和數(shù)據(jù)恢復(fù)(CDR)電路控制,該電路然后表現(xiàn)為數(shù)據(jù)系統(tǒng)中的握手.準(zhǔn)確接收和解釋數(shù)據(jù)的關(guān)鍵在于精確了解時鐘邊緣在任何時間點的”位置”.

由于發(fā)送和接收設(shè)備可以位于任何地方-從同一桌面到世界的另一端,因此每個不同的位置或環(huán)境都會影響時鐘晶振邊緣從發(fā)送數(shù)據(jù)到發(fā)送數(shù)據(jù)的時間如何漂移.設(shè)備接收和解釋數(shù)據(jù)的時間.這些影響很多,包括溫度,物理運動/振動,甚至是時鐘信號發(fā)起的架構(gòu).凈結(jié)果要么是否具有準(zhǔn)確數(shù)據(jù),否則“不”顯然不是任何系統(tǒng)中的選項.對于最終用戶而言,這可能意味著較差的體驗質(zhì)量以及對互聯(lián)網(wǎng)會話和相關(guān)服務(wù)的干擾(即語音質(zhì)量差,視頻內(nèi)容的觀看體驗不均勻或數(shù)據(jù)文件內(nèi)容損壞).性能特性是時鐘邊緣與預(yù)期精確度的精確度量,稱為“抖動”.通常在測量中使用三種抖動量化:

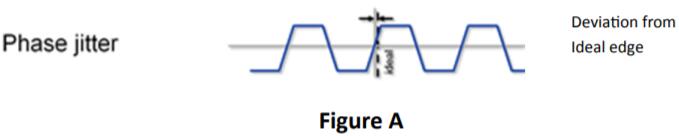

1.相位/RMS抖動-可被視為精細(xì)焦點測量.這通常稱為”絕對抖動”,即通過網(wǎng)絡(luò)分析儀測量信號的相位噪聲,通常顯示時鐘邊緣位置的總差異和整體差異(圖A);

2.峰值抖動和峰峰值抖動,每個抖動可被視為”過程”測量,并分為兩個特征:

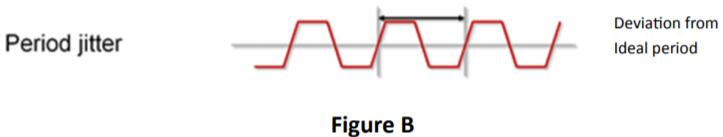

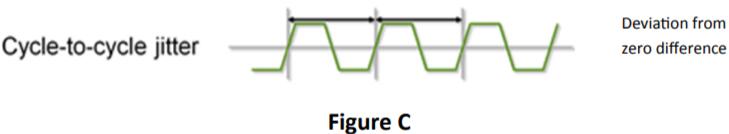

一個.周期抖動(又稱周期抖動)任何一個時鐘周期與理想或平均時鐘周期之間的差異-通常通過用示波器測量有源晶振信號周期來揭示(圖B),以及灣周期間抖動-任意兩個相鄰時鐘周期的持續(xù)時間差異.對于微處理器和RAM接口中使用的某些類型的時鐘生成電路而言,這也很重要,并且還可以使用示波器進行測量(圖C).抖動性能/規(guī)格限制已由ITU-T,Telcordia和IEEE等標(biāo)準(zhǔn)化機構(gòu)確定.本機以太網(wǎng)(IEEE)上的抖動規(guī)范和測試方法與SDH/SONET/SyncE(ITU-T,Telcordia)的規(guī)范和測試方法不同.

用于創(chuàng)建系統(tǒng)時鐘的流行基礎(chǔ)組件是石英晶體振蕩器(XO),這是一種已經(jīng)使用多年的技術(shù).晶體振蕩器本身具有固有的抖動特性,其輸出抖動將根據(jù)設(shè)計/電路和單價而變化.智能系統(tǒng)設(shè)計人員意識到系統(tǒng)/產(chǎn)品/設(shè)計的總成本本身就是一個需要滿足的“規(guī)范”.本文介紹了每種信號創(chuàng)建方法以及推薦表,以幫助潛在用戶承擔(dān)比必要更高的組件成本.

SYSCLK起源方法

基本的無褶邊晶體振蕩器采用石英晶體,并與簡單的電路一起使用,以在晶體的基本模式下運行,并創(chuàng)建方波輸出.該架構(gòu)為峰峰值和RMS抖動提供了最佳性能,在頻率高達50Mhz時通常是最具成本效益的.為了以盡可能低的抖動達到更高的頻率,使用稱為高頻基波(“HFF”)的技術(shù).可以使晶體以其泛音模式之一振動,這發(fā)生在基本諧振頻率的奇數(shù)倍數(shù)附近.這種晶體被稱為第3,第5,第7......等泛音(OT)晶體.為了實現(xiàn)這一點,振蕩器電路通常包括額外的設(shè)計元件以選擇所需的泛音.相關(guān)地,在典型的應(yīng)用中,可以有效地執(zhí)行使晶體在其第三泛音上工作以達到高達3x50Mhz=150Mhz的頻率的架構(gòu).

更高泛音的操作需要更復(fù)雜的電路,并且一些振蕩器公司正致力于增加石英晶體基本和第三泛音諧振技術(shù),以支持例如70.8333Mhzx3=212.500Mhz的10Gb光纖通道.這些努力的重點是提供最低的抖動主時鐘性能-隨著數(shù)據(jù)總線速度的不斷提高而需要.盡管如此,這項技術(shù)仍處于高級階段,所有晶體振蕩器供應(yīng)商都無法提供.

已經(jīng)成功使用的另一種技術(shù)是集成整數(shù)乘法器.在這些器件中,通過將輸入信號鎖定到以晶體頻率的直接整數(shù)倍(2x,3x,4x......等)運行的集成電壓控制振蕩器,然后二進制分頻回到所需的op-,可以提高頻率.降低頻率.可以采用的另一種方法是諧波乘法.這在技術(shù)上類似于晶體泛音利用,不同之處在于來自晶體振蕩器(不是晶體)的輸出信號乘以整數(shù)值.除了電路積分中的損耗和其他折衷之外,抖動性能比直接(即泛音模式的晶體基本)頻率產(chǎn)生的因子20LogN(其中N是整數(shù)倍增因子)惡化.

因此,盡管基頻,諧波和/或諧波頻率生成是可能的,但與集成整數(shù)乘法相比,這些技術(shù)通常成本和復(fù)雜性都是過高的,這可以滿足抖動要求,盡管余量較小.為了避免任何不必要的成本溢價,設(shè)計人員在設(shè)計裕量期間需要關(guān)注的是計算輸出信號抖動的特定帶寬.

所使用的第三種技術(shù)被稱為集成的分?jǐn)?shù)N乘數(shù).這是輸入信號的頻率可以轉(zhuǎn)換成幾乎任何其他相關(guān)的頻率-整數(shù)的地方.例如,25Mhz石英晶體諧振器頻率可以通過25.78125的分?jǐn)?shù)乘法轉(zhuǎn)換為644.53125Mhz.由于超出本文預(yù)期目的和深度的原因,這會導(dǎo)致最大量的信號抖動.同樣,它對于某些系統(tǒng)來說已經(jīng)足夠,并且在215Mhz以上的頻率下使用是最具成本效益的.

晶體振蕩器輸出邏輯

在前一節(jié)中,討論了生成CLK的方法及其如何影響抖動性能.無論實現(xiàn)架構(gòu)是基本結(jié)構(gòu)還是泛音晶體,N乘法器或分?jǐn)?shù)N乘法器,晶體振蕩器還包含依照現(xiàn)有邏輯技術(shù)的輸出驅(qū)動器.輸出邏輯兼容性的具體類型可以是低壓CMOS(LVCMOS),低壓,正電源發(fā)射極耦合邏輯(LVPECL),低壓差分晶體振蕩器信號(LVDS)和/或高速電流控制邏輯(HCSL).輸出邏輯類型主要與給定應(yīng)用類型內(nèi)的處理設(shè)備的邏輯接口的輸出頻率和/或通用性有關(guān).例如,PCIeSY SCLK的主要邏輯類型是HCSL.

晶體振蕩器輸出邏輯兼容性通常會使處理器件邏輯的開發(fā)滯后6到12個月,有時甚至更長.邏輯翻譯器在過渡期間使用.這種情況的一個例子是轉(zhuǎn)換最小化差分信令(TMDS).TMDS用于系統(tǒng)設(shè)計中的某些應(yīng)用(例如:HDMI),但目前不能作為晶體振蕩器輸出邏輯的選擇.輸出邏輯類型的重要性在于通過將石英振蕩器(和任何附加輸出轉(zhuǎn)換設(shè)備)連接到處理設(shè)備而引入的“接口抖動”的貢獻.通常,具有最快轉(zhuǎn)換時間(例如,上升/下降時間)到“眼圖”的邏輯類型將導(dǎo)致最低的接口抖動.

選擇最佳CLK時鐘源設(shè)備

無論性能規(guī)范,規(guī)范要求或特定的PHY芯片組/執(zhí)行方法如何,最重要的規(guī)范都是實現(xiàn)的成本效益.所有商業(yè)和工業(yè)系統(tǒng)都滿足所有性能要求,但總成本高于市場要求,沒有任何價值.

高速串行總線架構(gòu)是當(dāng)今高性能設(shè)計的標(biāo)準(zhǔn).雖然并行總線標(biāo)準(zhǔn)正在發(fā)生一些變化,但串行總線在多個市場和設(shè)備上建立-計算機,手機,娛樂系統(tǒng)等.串行總線在電路和電路板布局中提供了性能優(yōu)勢和設(shè)計簡化(更少的跡線).串行數(shù)據(jù)鏈路表現(xiàn)為當(dāng)今知情世界的動脈,因為它們在處理系統(tǒng)中將數(shù)據(jù)從一個點傳輸?shù)搅硪粋€點.為了確保準(zhǔn)確的傳送和接收,數(shù)字系統(tǒng)中的數(shù)據(jù)由時鐘和數(shù)據(jù)恢復(fù)(CDR)電路控制,該電路然后表現(xiàn)為數(shù)據(jù)系統(tǒng)中的握手.準(zhǔn)確接收和解釋數(shù)據(jù)的關(guān)鍵在于精確了解時鐘邊緣在任何時間點的”位置”.

由于發(fā)送和接收設(shè)備可以位于任何地方-從同一桌面到世界的另一端,因此每個不同的位置或環(huán)境都會影響時鐘晶振邊緣從發(fā)送數(shù)據(jù)到發(fā)送數(shù)據(jù)的時間如何漂移.設(shè)備接收和解釋數(shù)據(jù)的時間.這些影響很多,包括溫度,物理運動/振動,甚至是時鐘信號發(fā)起的架構(gòu).凈結(jié)果要么是否具有準(zhǔn)確數(shù)據(jù),否則“不”顯然不是任何系統(tǒng)中的選項.對于最終用戶而言,這可能意味著較差的體驗質(zhì)量以及對互聯(lián)網(wǎng)會話和相關(guān)服務(wù)的干擾(即語音質(zhì)量差,視頻內(nèi)容的觀看體驗不均勻或數(shù)據(jù)文件內(nèi)容損壞).性能特性是時鐘邊緣與預(yù)期精確度的精確度量,稱為“抖動”.通常在測量中使用三種抖動量化:

1.相位/RMS抖動-可被視為精細(xì)焦點測量.這通常稱為”絕對抖動”,即通過網(wǎng)絡(luò)分析儀測量信號的相位噪聲,通常顯示時鐘邊緣位置的總差異和整體差異(圖A);

2.峰值抖動和峰峰值抖動,每個抖動可被視為”過程”測量,并分為兩個特征:

一個.周期抖動(又稱周期抖動)任何一個時鐘周期與理想或平均時鐘周期之間的差異-通常通過用示波器測量有源晶振信號周期來揭示(圖B),以及灣周期間抖動-任意兩個相鄰時鐘周期的持續(xù)時間差異.對于微處理器和RAM接口中使用的某些類型的時鐘生成電路而言,這也很重要,并且還可以使用示波器進行測量(圖C).抖動性能/規(guī)格限制已由ITU-T,Telcordia和IEEE等標(biāo)準(zhǔn)化機構(gòu)確定.本機以太網(wǎng)(IEEE)上的抖動規(guī)范和測試方法與SDH/SONET/SyncE(ITU-T,Telcordia)的規(guī)范和測試方法不同.

抖動生成

隨著下一代串行標(biāo)準(zhǔn)的數(shù)據(jù)速率的提高,模擬異常對信號完整性和質(zhì)量的影響比以往任何時候都大.信號路徑中的導(dǎo)體,包括電路板走線,過孔,連接器和布線,表現(xiàn)出更大的傳輸線效應(yīng),回波損耗和反射會降低信號電平,引起偏移,并增加噪聲,從而產(chǎn)生抖動.然而,一切都始于基本系統(tǒng)時鐘信號(SYSCLK或主時鐘).除了時鐘信號的顯著性能特征之外,創(chuàng)建信號的成本可以在10倍以上變化-取決于所使用的架構(gòu)和設(shè)計方法.為了幫助實現(xiàn)沒有過多性能保護帶的系統(tǒng)設(shè)計(因此成本過高),本文重點介紹用于創(chuàng)建符合每個特定高速串行數(shù)據(jù)(HSSD)的時鐘信號的不同架構(gòu)的更新.實施方案.特定的抖動類型,定義和一致性測試方法已經(jīng)有很好的文檔記錄,這里不再重復(fù).用于創(chuàng)建系統(tǒng)時鐘的流行基礎(chǔ)組件是石英晶體振蕩器(XO),這是一種已經(jīng)使用多年的技術(shù).晶體振蕩器本身具有固有的抖動特性,其輸出抖動將根據(jù)設(shè)計/電路和單價而變化.智能系統(tǒng)設(shè)計人員意識到系統(tǒng)/產(chǎn)品/設(shè)計的總成本本身就是一個需要滿足的“規(guī)范”.本文介紹了每種信號創(chuàng)建方法以及推薦表,以幫助潛在用戶承擔(dān)比必要更高的組件成本.

SYSCLK起源方法

基本的無褶邊晶體振蕩器采用石英晶體,并與簡單的電路一起使用,以在晶體的基本模式下運行,并創(chuàng)建方波輸出.該架構(gòu)為峰峰值和RMS抖動提供了最佳性能,在頻率高達50Mhz時通常是最具成本效益的.為了以盡可能低的抖動達到更高的頻率,使用稱為高頻基波(“HFF”)的技術(shù).可以使晶體以其泛音模式之一振動,這發(fā)生在基本諧振頻率的奇數(shù)倍數(shù)附近.這種晶體被稱為第3,第5,第7......等泛音(OT)晶體.為了實現(xiàn)這一點,振蕩器電路通常包括額外的設(shè)計元件以選擇所需的泛音.相關(guān)地,在典型的應(yīng)用中,可以有效地執(zhí)行使晶體在其第三泛音上工作以達到高達3x50Mhz=150Mhz的頻率的架構(gòu).

更高泛音的操作需要更復(fù)雜的電路,并且一些振蕩器公司正致力于增加石英晶體基本和第三泛音諧振技術(shù),以支持例如70.8333Mhzx3=212.500Mhz的10Gb光纖通道.這些努力的重點是提供最低的抖動主時鐘性能-隨著數(shù)據(jù)總線速度的不斷提高而需要.盡管如此,這項技術(shù)仍處于高級階段,所有晶體振蕩器供應(yīng)商都無法提供.

已經(jīng)成功使用的另一種技術(shù)是集成整數(shù)乘法器.在這些器件中,通過將輸入信號鎖定到以晶體頻率的直接整數(shù)倍(2x,3x,4x......等)運行的集成電壓控制振蕩器,然后二進制分頻回到所需的op-,可以提高頻率.降低頻率.可以采用的另一種方法是諧波乘法.這在技術(shù)上類似于晶體泛音利用,不同之處在于來自晶體振蕩器(不是晶體)的輸出信號乘以整數(shù)值.除了電路積分中的損耗和其他折衷之外,抖動性能比直接(即泛音模式的晶體基本)頻率產(chǎn)生的因子20LogN(其中N是整數(shù)倍增因子)惡化.

因此,盡管基頻,諧波和/或諧波頻率生成是可能的,但與集成整數(shù)乘法相比,這些技術(shù)通常成本和復(fù)雜性都是過高的,這可以滿足抖動要求,盡管余量較小.為了避免任何不必要的成本溢價,設(shè)計人員在設(shè)計裕量期間需要關(guān)注的是計算輸出信號抖動的特定帶寬.

所使用的第三種技術(shù)被稱為集成的分?jǐn)?shù)N乘數(shù).這是輸入信號的頻率可以轉(zhuǎn)換成幾乎任何其他相關(guān)的頻率-整數(shù)的地方.例如,25Mhz石英晶體諧振器頻率可以通過25.78125的分?jǐn)?shù)乘法轉(zhuǎn)換為644.53125Mhz.由于超出本文預(yù)期目的和深度的原因,這會導(dǎo)致最大量的信號抖動.同樣,它對于某些系統(tǒng)來說已經(jīng)足夠,并且在215Mhz以上的頻率下使用是最具成本效益的.

晶體振蕩器輸出邏輯

在前一節(jié)中,討論了生成CLK的方法及其如何影響抖動性能.無論實現(xiàn)架構(gòu)是基本結(jié)構(gòu)還是泛音晶體,N乘法器或分?jǐn)?shù)N乘法器,晶體振蕩器還包含依照現(xiàn)有邏輯技術(shù)的輸出驅(qū)動器.輸出邏輯兼容性的具體類型可以是低壓CMOS(LVCMOS),低壓,正電源發(fā)射極耦合邏輯(LVPECL),低壓差分晶體振蕩器信號(LVDS)和/或高速電流控制邏輯(HCSL).輸出邏輯類型主要與給定應(yīng)用類型內(nèi)的處理設(shè)備的邏輯接口的輸出頻率和/或通用性有關(guān).例如,PCIeSY SCLK的主要邏輯類型是HCSL.

晶體振蕩器輸出邏輯兼容性通常會使處理器件邏輯的開發(fā)滯后6到12個月,有時甚至更長.邏輯翻譯器在過渡期間使用.這種情況的一個例子是轉(zhuǎn)換最小化差分信令(TMDS).TMDS用于系統(tǒng)設(shè)計中的某些應(yīng)用(例如:HDMI),但目前不能作為晶體振蕩器輸出邏輯的選擇.輸出邏輯類型的重要性在于通過將石英振蕩器(和任何附加輸出轉(zhuǎn)換設(shè)備)連接到處理設(shè)備而引入的“接口抖動”的貢獻.通常,具有最快轉(zhuǎn)換時間(例如,上升/下降時間)到“眼圖”的邏輯類型將導(dǎo)致最低的接口抖動.

選擇最佳CLK時鐘源設(shè)備

無論性能規(guī)范,規(guī)范要求或特定的PHY芯片組/執(zhí)行方法如何,最重要的規(guī)范都是實現(xiàn)的成本效益.所有商業(yè)和工業(yè)系統(tǒng)都滿足所有性能要求,但總成本高于市場要求,沒有任何價值.

正在載入評論數(shù)據(jù)...

此文關(guān)鍵字: 低抖動晶體振蕩器高性能晶振設(shè)計

- [2023-09-26]臺灣SIWARD晶振有著領(lǐng)先全球的光蝕刻制...

- [2023-07-12]淺談決定差分石英晶體振蕩器的振蕩頻率...

- [2023-06-27]SMD時鐘硅振蕩器從0/+70°c到-55/+125°...

- [2023-06-20]GPS接收器專用溫補晶體振蕩器C34-040.0...

- [2023-06-17]Cardinal石英晶體CSM1Z-A5B2C5-40-25.0...

- [2023-06-13]Aker音叉晶體CTS3-32.768-9-20-R為何開...

- [2023-02-16]具備高品質(zhì)的石英晶體用于無線通信CS-0...

- [2022-09-16]EPSON蘋果手機無線充電器專用晶振Q3805...

- [2022-08-04]Abracon生產(chǎn)非常適合微處理器的時鐘晶體...

- [2022-08-03]西迪斯設(shè)計出獨特性能的小型化時鐘振蕩...

- [2022-08-02]村田首推用于消費級的陶瓷諧振器CSTLS8...

- [2022-07-22]常用編碼KC3225K12.0000C1GE00是一款微...

銷售代表

銷售代表 售后服務(wù)

售后服務(wù)